# 0.75V ESD power protection – TSMC 3nm Enhanced

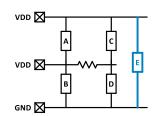

ESD Device - Type E

ESD power protection

Cell name: ZZ\_075\_V\_Rail\_PS\_0

The ESD clamp is designed to provide 8kV HBM protection for 0.75 V Analog and Core domain using 0.75V FinFet transistors in TSMC N3E process.

This clamp is selected for the protection of the following specific application:

0.75V Power domain using 0.75V FinFet transistors.

#### Features:

- Efficient ESD power protection

- O Up to ± 8 kV Human Body Model (HBM)

- Up to ± 1 kV Charged Device Model (CDM)

- o Latch-Up safe

#### **Circuit schematic:**

### **MAXIMUM RATINGS**

| Rating                     | Symbol   | Value |      | Unit |

|----------------------------|----------|-------|------|------|

|                            |          | Min   | Max  |      |

| Supply Voltage Range (DC)  | $V_{DD}$ | -0.3  | 1.32 | V    |

| Max. Operating Temperature |          | 125   |      | °C   |

Stresses exceeding these maximum ratings may damage the device. Functional operation above the recommended operating conditions is not implied. Extended exposure to stresses above the recommended operating conditions may affect device reliability.

The provided golden cell is designed for these maximum ratings/specifications. If the desired specification level differs, the golden cell has to be scaled up or down by using the Sofics implementation/scaling guidelines to remain a robust and effective ESD protection for the different specifications.

# **ELECTRICAL CHARACTERISTICS** (T<sub>amb</sub> = 25°C unless stated otherwise)

| Parameter                        | Symbol              | Min.            | Тур. | Max.            | Unit |

|----------------------------------|---------------------|-----------------|------|-----------------|------|

| Supply Voltage                   | $V_{DD}$            | - 0.3           | 0.75 | 1.08            | V    |

| Trigger Voltage                  | V <sub>t1</sub>     | -               | 0.5  | -               | V    |

| Breakdown Voltage                | V <sub>t2</sub>     | -               | 5.3  | -               | V    |

| Maximum Current                  | I <sub>max</sub>    | -               | > 10 | -               | Α    |

| On-Resistance                    | Ron                 | 0.4             | 0.48 | 0.6             | Ohm  |

| Reverse Voltage                  | V <sub>rev</sub>    | -               | 1    | -               | V    |

| Maximum Current of Reverse Diode | I <sub>max,RD</sub> | -               | > 10 | -               | Α    |

| On-Resistance of Reverse Diode   | Ron                 | 0.4             | 0.48 | 0.6             | Ohm  |

| Operating Temperature Range      | T <sub>op</sub>     | -40             | -    | +125            | °C   |

| HBM – Human Body Model           |                     | -2 till -8      | -    | +2 till +8      | kV   |

| CDM – Charged Device Model       |                     | -250 till -1000 | -    | +250 till +1000 | V    |

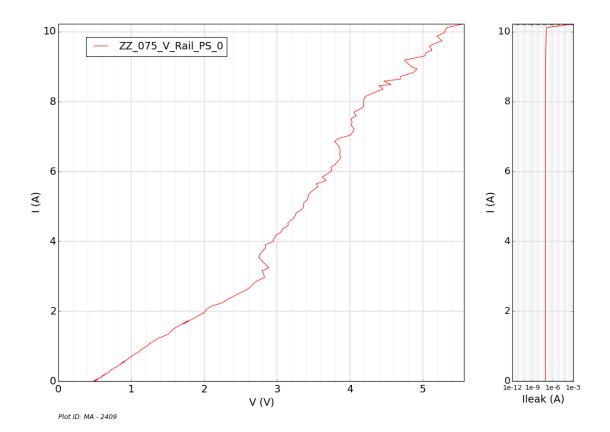

# TLP I-V

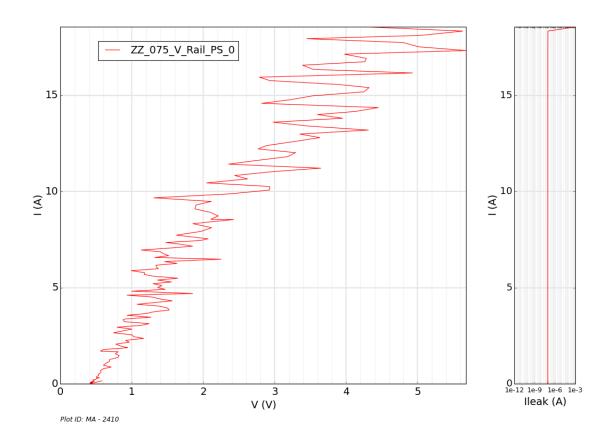

# VF-TLP I-V

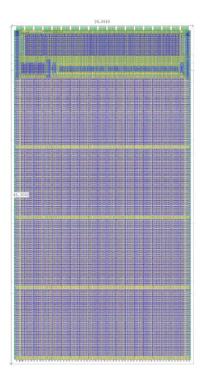

## LAYOUT/DIMENSIONS: ZZ\_075\_V\_Rail\_PS\_0

- Process: TSMC 3nm FinFet Enhanced

- Used Metals: 1P15M\_1Xa\_h\_1Xb\_v\_1Xc\_h\_1Xd\_v\_1Ya\_h\_1Yb\_v\_4Y\_hvhv\_2Yy2Z

- Required Special Layer: /

- Area:

- 8kV: 1151.3μm² (24.864μm x 46.306μm)

- $\circ$  6kV: 911.9 $\mu$ m<sup>2</sup> (24.864 $\mu$ m x 36.674 $\mu$ m)

- $\circ$  4kV: 680.3 $\mu$ m<sup>2</sup> (24.864 $\mu$ m x 27.361 $\mu$ m)

- 2kV: 432.9μm² (24.864μm x 17.410μm)

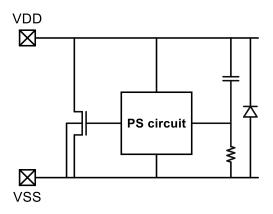

#### **CONNECTION GUIDELINES**

- 2 paths are required to be connected:

- o VDD: power, highest potential of domain to be protected

- o VSS: ground, lowest potential of domain to be protected

- All buses in the clamp can be used as feed-through buses.

- P+ guardbands are connected to VSS (ESD clamp is not isolated from substrate).

Respect the repetition rate/maximum allowed bus resistance when connecting with a power clamp in order to ensure the ESD robustness!

The maximum bus resistance should not exceed 0.8  $\Omega$  between 2 power clamps.